ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

## DESIGN AND ANALYSIS OF MODULAR MULTILEVEL CONVERTER FOR SOLAR PHOTOVOLTAIC APPLICATIONS TO IMPROVE POWER QUALITY

Madala Raviteja, Assistant Professor, Hyderabad Institute of Technology and Management, Medchal, Hyderabad, 501401, India <u>ravitejam.eee@hitam.org</u>;

C. Mahalakshmi, U.G Scholar, Hyderabad Institute of Technology and Management, Medchal, Hyderabad, 501401, India <u>22e55a0204@hitam.org</u>

A. Rahul, U.G Scholar, Hyderabad Institute of Technology and Management, Medchal, Hyderabad, 501401, India <u>rahulmudhirajs36@gmail.com</u>

**G. Shanmukh** U.G Scholar, Hyderabad Institute of Technology and Management, Medchal, Hyderabad, 501401, India <u>21e51a0209@hitam.org</u>

#### Abstract

Inverters are in high demand today due to their broad applicability. Based on the area of use, various types of inverters are available, with the Cascade H-bridge multilevel inverter being highly effective for industrial, power system, and household applications. Traditional two-level inverters have several limitations, including harmonic distortion and rapid voltage fluctuations in output. To address this, techniques to reduce harmonics have been developed. One of the most efficient methods involves using a cascade connection of H-bridges, which mitigates voltage fluctuations between levels, solving issues faced by traditional two-level inverters. This project explores the Cascade H-Bridge multilevel inverter, where multiple DC sources and numerous switches are utilized to minimize the voltage difference between levels. MATLAB simulations demonstrate that increasing the levels of a Cascade H-Bridge multilevel inverter results in an output waveform closely resembling a sine wave.

#### 1. Introduction

The Cascade H-Bridge inverter consists of a series connection of H-bridge modules. In this design, Hbridges are cascaded within each phase, and the combined output voltage produces a stepped waveform. As more H-bridges are added, the waveform becomes increasingly sinusoidal. In an n-level configuration, (n-1)/2 identical H-bridges are used per phase, with each module requiring its DC source. This topology is well-suited for renewable energy systems like solar panels and fuel cells, as it facilitates modular energy collection.

Renewable energy is becoming more prevalent in the grid, driven by the need for green energy. As energy demand rises, additional power generation and transmission infrastructure are required. Photovoltaic panels are a distributed energy source that can be installed at individual sites, such as rooftops. These panels use single-phase inverters to convert DC power into regulated AC power for loads. Power electronic converters play a vital role in generating AC voltage from DC sources, enabling connection to the grid.

Given the high total harmonic distortion (THD) and power losses of conventional two- and three-level inverters, as well as advancements in semiconductor switches, a new generation of multilevel inverters has emerged. These devices combine DC sources and switches to deliver superior performance. By producing a higher number of output voltage levels, multilevel inverters achieve smoother waveforms closer to a pure sinusoid.

#### 2.Objectives

The objective is the design and analysis of a modular multilevel converter for photovoltaic applications to improve power quality.

Developing and evaluating a Cascaded H-Bridge Multilevel Inverter (CHBMLI):

Addressing power quality issues such as harmonic reduction and voltage fluctuation.

Enhancing renewable energy integration:

Utilizing modular multilevel converters for better performance in solar photovoltaic systems.

#### UGC CARE Group-1

۲

ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

Simulation and analysis: Using MATLAB to simulate and optimize multilevel inverter designs for improved efficiency and output waveform quality.

#### 1. Methodology

## **1.**Components Specifications

1.1 DC Voltage Source

Amplitude: 100V

Rating: 100 W

Type: Monocrystalline

Maximum Power voltage (Vmp): 35-36 V Current at Maximum Power (Imp): 2.77 A

Open circuit voltage:40V

Open circuit voltage:40

Short circuit :3.35A

Operating temperature: -40°C to 85°C

# Efficiency:15-20% **1.2 MOSFET Switch**

Configured in pairs for each H-bridge module to control power flow.

FET resistance Ron (Ohms):  $0.1 \Omega$

Internal diode resistance Rd (Ohms): 0.01  $\Omega$

Snubber resistance Rs (Ohms): 1e5  $\Omega$

## **1.3 OR Gate Operator**

Ensures correct logic operation in the switching mechanism.

To control and synchronize the gate signals applied to MOSFETs.

## **1.4 Pulse Generator**

Type: PWM (Pulse Width Modulation) controller

Generates gate pulses to control the MOSFET switches.

Adjustable frequency and duty cycle

Synchronization with input DC voltage and output load requirements.

# **1.5 Cascaded H-Bridge Connection**

Consists of multiple H-bridge modules connected in series.

Each module operates at a different voltage level.

#### 1.6 Resistor

$100\Omega$

Acts as a load for testing and stabilizing the circuit output.

#### **1.7 Voltage Measurement**

Connected across the load resistor.

Compatible with the expected output voltage range.

# **1.8 Scope for Output**

Monitors voltage levels and harmonic content.

Displays time-domain signals.

# **1.9 PowerGUI**

Simulation tool in MATLAB/Simulink.

Allows time-domain and frequency-domain analysis.

Handles steady-state and dynamic conditions.

# 2. System & design

ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

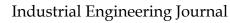

Fig 2.2.1 Ciruit diagram

| Output<br>Voltage | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 |

|-------------------|----|----|----|----|----|----|

| +Vdc              | 1  | 0  | 0  | 1  | 0  | 0  |

| +2Vdc/3           | 0  | 0  | 0  | 1  | 1  | 0  |

| +Vdc/3            | 0  | 0  | 0  | 1  | 0  | 1  |

| 0                 | 0  | 0  | 1  | 1  | 0  | 0  |

| 0*                | 1  | 1  | 0  | 0  | 0  | 0  |

| -Vdc/3            | 0  | 1  | 0  | 0  | 1  | 0  |

| -2Vdc/3           | 0  | 1  | 0  | 0  | 0  | 1  |

| -Vdc              | 0  | 1  | 1  | 0  | 0  | 0  |

#### Fig 2.2.2 Truth table

The inverter's topology relies on connecting single-phase modules with independent DC sources. Phase voltage is synthesized by summing the output voltages of individual cells. For example, in a five-level cascaded inverter, each module can generate output levels such as +Vdc, 0, and -Vdc. The resulting staircase waveform closely mimics a sinusoid without filtering.

The growing use of multilevel inverters across industries, homes, railways, and power systems stems from their ability to deliver high-voltage levels, enhance efficiency, minimize switching stress, reduce filter costs, and generate smooth output waveforms. The main advantages of multilevel inverters are: 1. Suitable for high-voltage, high-power applications.

- 2. Reduces total harmonic distortion (THD).

- 2. Reduces total harmonic distortion (THD

- 3. Minimizes switching stress.

- 4. Simplifies layout designs for manufacturing.

5. Uses a staircase waveform to approximate pure sinusoidal output as levels increase.

The output of five-level cascade H-bridge inverters is more reliable, with reduced switching stress and superior fault tolerance compared to other inverter topologies.

# 3. MATLAB Design and simulation

ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

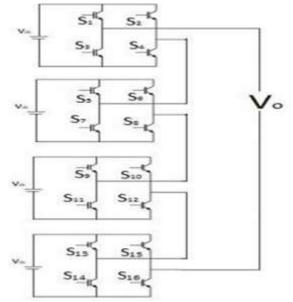

Fig 2.3.1 Simulation diagram of battery charging using solar panel

Sinusoidal or other waveform signal generators are shown on the top. These signals act as reference inputs for controlling the switches. Each input signal is fed into a control/modulation block (marked as amplifiers or comparators). These units generate switching signals for the power switches (likely PWM signals). The circuit contains multiple switches (likely IGBTs or MOSFETs) arranged in several H-bridge or cascaded configurations. Each switch group has a parallel diode, which might work as a freewheeling diode for reactive power compensation. Capacitors are connected across the switches, indicating the presence of DC bus segments. These segments store and regulate DC voltage levels for the inverter. The circuit includes multiple such levels connected in series. This indicates it is a multilevel converter (like a cascaded H-bridge or diode-clamped multilevel topology). The outputs of all switch stages are combined and connected to a resistive component, likely representing a load. On the far-right, there's a control or monitoring block to process or manage the output.

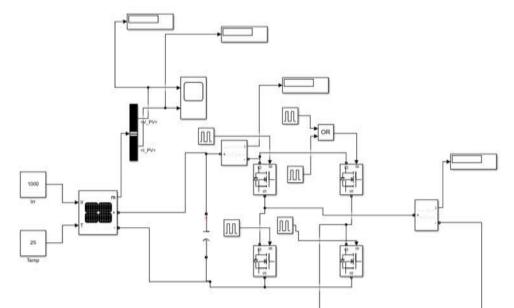

# 4. DESIGN & IMPLEMENTATION

Fig 2.4.1 Pin Configuration

Industrial Engineering Journal ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

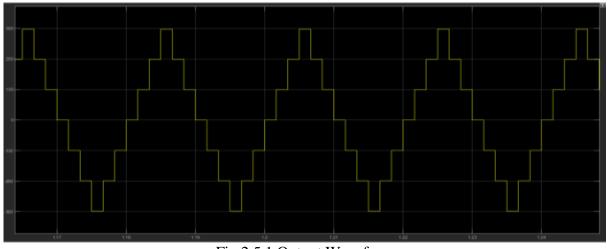

Fig 2.5.1 Output Waveform

The output voltage of this inverter comprises five distinct levels, similar to other multilevel inverter designs. It operates using two H-bridge inverters connected in series. For a five-level cascaded H-bridge inverter, eight switching devices are required.

As depicted in Fig 2.5, the inverter consists of two H-bridge circuits with a series connection, each powered by a separate DC voltage source. Each H-bridge circuit uses four MOSFET switches, resulting in a total of eight for the entire system. The two H-bridges are operated as series-connected units, where the switches in the first H-bridge (S1, S4) and the second H-bridge (S1', S4') close simultaneously while others remain off. This configuration produces a stepped waveform at the output. Adding more levels increases the required DC sources and the system's complexity and cost, posing significant design challenges.

Multilevel inverters are frequently used in applications where high power and superior power quality are crucial, such as uninterruptible power supplies (UPS), photovoltaic power systems, and hybrid powertrains.

To analyze the five-level inverter design in MATLAB, the modulation index—a measure of the ratio between the modulation and carrier waveforms' peak amplitudes—is first determined. This index directly relates to the inverter's DC-link voltage. A sine wave (the reference signal) is compared to four triangular carrier waves of varying amplitudes, producing pulse waveforms. These waveforms form the basis for PWM (Pulse Width Modulation), generating signals to control the inverter switches. Following this, FFT analysis is performed to evaluate system performance.

# Conclusion

The cascaded H-bridge multilevel inverter is a promising topology for applications requiring highpower and high voltage power conversion. It has the capability to synthesize a wide range of output voltages and is suitable for both high-power industrial and low-power residential applications. Furthermore, it is capable of operating with reduced harmonic distortion and offers a lower total harmonic distortion than other multilevel inverters. The cascaded multilevel inverter is also able to adjust the DC bus voltage and increase the power efficiency in the power grid, making it an attractive option for use in renewable energy systems.

# References

[1] S. Kouro et al., "Recent Advances and Industrial Applications of Multilevel Converters," in IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

[2] Surin Khomfoi and Leon M. Tolbert, Ph.D., "Multilevel Power Converters", Power Electronics Handbook, The University of Tennessee, Department of Electrical and Computer Engineering, Knoxville, Tennessee, USA

ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

[3] Rodriguez, J.; Jih-Sheng Lai; Fang Zheng Peng; , "Multilevel inverters: a survey of topologies, controls, and applications," Industrial Electronics, IEEE Transactions on , vol.49, no.4, pp. 724-738, Aug 2002

[4] Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A.;, "A Survey on Cascaded Multilevel Inverters," Power Electronics, IEEE Transactions on , vol.57, no.7 pp.2197-2206, July 2010

[5] D. S. Ochs, B. Mirafzal and P. Sotoodeh, "A Method of Seamless Transitions Between Grid-Tied and Stand-Alone Modes of Operation for Utility-Interactive Three-Phase Inverters," in IEEE Transactions on Industry Applications, vol. 50, no. 3, pp. 1934-1941, May-June 2014.

[6] G. J. M. de Sousa, A. d. S. Dias, J. A. Alves and M. L. Heldwein, "Modeling and control of a Modular Multilevel Converter for medium voltage drives rectifier applications," 2015 IEEE 24th International Symposium on Industrial Electronics (ISIE), Buzios, 2015, pp. 1080-1087.

[7] F. Badrkhani Ajaei and R. Iravani, "Dynamic Interactions of the MMC-HVDC Grid and its Host AC System Due to AC-Side Disturbances," in IEEE Transactions on Power Delivery, vol. 31, no. 3, pp. 1289-1298, June 2016.

[8] M. M. Swamy, J. K. Kang and K. Shirabe, "Power Loss, System Efficiency, and Leakage Current Comparison Between Si IGBT VFD and SiC FET VFD With Various Filtering Options," in IEEE Transactions on Industry Applications, vol. 51, no. 5, pp. 3858-3866, Sept.-Oct. 2015.

[9] F. Haase, A. Kouchaki and M. Nymand, "Controller design and implementation of a three-phase Active Front End using SiC based MOSFETs," 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, 2015, pp. 2681-2687.

[10] S. Bernet, "State of the art and developments of medium voltage converters—An overview," Prz. Elektrotech. (Electr. Rev.), vol. 82, no. 5, pp. 1–10, May 2006.

[11] Y. Shakweh, "MV inverter stack topologies," IEE Power Eng. J., vol. 15, no. 3, pp. 139–149, Jun. 2001.

[12] R. Marquardt, Modular multilevel converter: An universal concept for HVDC-networks and extended DC-bus-applications, in Proc. Int. Power Electron. Conf. (ECCE ASIA), Sapporo, Japan, Jun. 2010, pp. 502 507.

[13] M. A. Perez, S. Bernet, J. Rodriguez, S. Kouro, and R. Lizana, Circuit topologies, modeling, control schemes, and applications of modular mul tilevel converters, IEEE Trans. Power Electron., vol. 30, no. 1, pp. 417, Jan. 2015, doi: 10.1109/TPEL.2014.2310127.

[14] J. Qin, M. Saeedifard, A. Rockhill, and R. Zhou, Hybrid design of mod ular multilevel converters for HVDC systems based on various submodule circuits, IEEE Trans. Power Del., vol. 30, no. 1, pp. 385394, Feb. 2015, doi: 10.1109/TPWRD.2014.2351794.

[15] L. Huang, X. Yang, P. Xu, F. Zhang, X. Ma, T. Liu, X. Hao, and W. Liu, The evolution and variation of sub-module topologies with DC-fault current clearing capability in MMC-HVDC, inProc.IEEE3rdInt.Future Energy Electron. Conf. ECCE Asia (IFEEC-ECCE Asia), Kaohsiung, Taiwan, Jun. 2017, pp. 19381943

[16] M. M. C. Merlin, T. C. Green, P. D. Mitcheson, D. R. Trainer, R. Critchley, W. Crookes, and F. Hassan, The alternate arm converter: A new hybrid multilevel converter with DC-fault blocking capabil ity, IEEE Trans. Power Del., vol. 29, no. 1, pp. 310317, Feb. 2014, doi: 10.1109/TPWRD.2013.2282171.

[17] Guide for the Development of Models for HVDC Converters in a HVDC Grid, Cigré Working Group, Technol. Brochure, Dec. 2014.

[18] M. Barnes, D. Van Hertem, S. P. Teeuwsen, and M. Callavik, HVDC systems in smart grids, Proc. IEEE, vol. 105, no. 11, pp. 20822098, Nov. 2017, doi: 10.1109/JPROC.2017.2672879.

[19] K. Eriksson. (2001). HVDC Light and Development of Voltage Source Converters. ABB, Zürich, Switzerland. [Online]. Available: https://library.e.abb.com/public/1f9325bfc027ca6dc1256fda004c8cbb/

HVDC% 20Light% 20and% 20development% 20of% 20VSC.pdf

UGC CARE Group-1

ISSN: 0970-2555

Volume : 54, Issue 3, No.3, March : 2025

[20] X. Xiang, M. M. C. Merlin, and T. C. Green, Cost analysis and compar ison of HVAC, LFAC and HVDC for offshore wind power connection, in Proc. 12th IET Int. Conf. AC DC Power Transmiss. (ACDC), Beijing, China, May 2016, pp. 16.

[21] Imperix. [Online]. Accessed: Apr. 28, 2020. Available: https://imperix.ch/

[22] Opal-RT Worldwide Leadership in Modular Multilevel Converter Test ing. Accessed: Apr. 28, 2020. [Online]. Available: https://www.opal.rt.com/modular-multilevel-converter/

[23] W. Zhou, J. Sheng, H. Luo, W. Li, and X. He, Detection and localiza tion of submodule opencircuit failures for modular multilevel converters with single ring theorem, IEEE Trans. Power Electron., vol. 34, no. 4, pp. 37293739, Apr. 2019, doi: 10.1109/TPEL.2018.2849441.

[24] S. Lu, L. Yuan, K. Li, and Z. Zhao, An improved phase-shifted car rier modulation scheme for a hybrid modular multilevel converter, IEEE Trans. Power Electron., vol. 32, no. 1, pp. 8197, Jan. 2017,